Base de données :

Regroupe les données nécessaires à la réalisation

d'un ASIC. Se présente sous forme d'une structure de fichiers. C'est une base de données qui est remise au fondeur en vue

de la fabrication d'un circuit. Le fondeur procčde en principe ŕ une ultime vérification de la cohérence de cette base de données.

Il vérifie tout particuličrement la compatibilité avec le processus de fabrication et les caractéristiques technologiques de sa chaine

de fonderie.

Début

DébutB.C.D : Binary Coded Decimal. Ou décimal codé binaire en francais.

Consiste ŕ coder chaque chiffre d'un nombre décimal en binaire. Ainsi:

14 est codé en base 2: 1 1 1 0.

14 est codé en BCD: 0001 0100.

B.C.E : Banque Centrale Européenne (Celle qui nous mčne la vie dure)

Bibliothèque : (LIBRARY)

Ensemble des fichiers descriptifs des cellules élémentaires mises à la disposition d'un client pour mener à bien la conception

de son circuit. Le client procéde dans un "éditeur de schéma" à une interconnexion de ces cellules (netlist). Les descriptions

vont des fonctionnalités de la cellule pour simulations logiques aux layouts des cellules en passant par les données technologiques

intervenant dans les simulations rétro-annotées.

B.I.O.S : Basic Input Output System. C'est le controleur des entrées / sorties au coeur de votre ordinateur.

A chaque mise sous tension le BIOS est transféré d'une mémoire morte en mémoire vive de l'ordinateur pour prendre le controle de la machine en chargeant le systčme d'exploitation.

B.L.M : Behavioral Language Model. Langage de description du comportement d'un bloc. On utilise souvent VHDL ou Verilog.

BLOG : Contraction de weB LOG

Bonder :

Machine effectuant le "bonding". Raccordement des pads du die

(pad ring) aux broches du boitier à l'aide de fils dorés pour une conductibilité maximale.

Eu égard aux fréquences élevées de communication d'un boitier ŕ l'autre, ces fils, pour aussi courts qu'ils soient, présentent un effet selfique.

Boundary-Scan : Chainage en décalages sur la périphérie (Frontičre). Voir J.T.A.G.

Electronique spécifique au niveau des plots d'entrée / sortie améliorant la testabilité au niveau carte. Peut

ètre associé aux scan-path internes pour le test interne.

Breakpoint : Point d'arret. On insčre des points d'arret dans les étapes de simulations.

C'est la possibilité d'arréter une simulation sur vérification d'une condition donnée

(exemple: signal N à l'état bas ET VAL à l'état haut).

BRIC: Brésiliens Russes Indiens Chinois. Les nouveaux touristes qui ne sauraient manquer de visiter notre pays.

BiCMOS : Bipolaire et CMOS. Technologie aliant transistors bipolaires et transistors MOS. Les transistors MOS pour le traitement logique. Les bipolaires pour l'interfacage rapide avec les autres cellules.

Burn-in : Procédure de déverminage des composants consistant entre autres à accélérer leur vieillissement pour mesurer leur fiabilité.

BYPASS : Instruction définie dans le standard du Boundary-Scan autorisant le passage par le registre de BY-PASS.

B-ISDN : Broadband Integrated Services Digital Network.

Début

DébutC : Langage de programmation développé par AT&T Bell Laboratories.

C.A.D : Computer Aided Design.

C.A.M : Content Addressable Memory

Mémoire adressable par le contenu (applications: Parcours des arborescences,

gestion bases de données,.... )

C.A.N : Convertisseur Analogique Numérique

C.A.O : Conception Assistée par Ordinateur.

Désigne l'ensemble des outils informatiques mis à la disposition d'un concepteur.

Caractérisation:

Etape de mesures et de test des performances des cellules mises à

la disposition d'un concepteur. Ces relevés se feront pour tous

les cas de figure d'utilisation (conditions pire-cas en température, alimentation et process).

Cavité : Emplacement du boitier ou la puce est fixée .

Cellule : (CELL) Opérateur élémentaire défini jusqu'au niveau de son layout. C'est l'entité de base de toute structure logique.

Charge : (Load)

Somme des capacités vues en sortie d'un opérateur logique

(Charges capacitives des entrées connectées, pistes d'interconnexion,

propres capacités de sortie de l'opérateur lui-mème).

C.E.M.I.P : Centre de Microélectronique de Paris Ile de France

Pole du C.N.F.M (Comité National de Formation en Microélectronique)

CERDIP : Type de boitier DIP céramique

standard plus particulièrement utilisé dans les applications militaires et spaciales.

Début

DébutC.F.A.O Création et Fabrication Assistées par Ordinateur.

C.G.A Color Graphic Adapter.

C.I : Circuit Intégré

C.I.M.E : Centre Interuniversitaire de Microélectronique.

C.I.F : Caltech Intermediate Form

Langage de description synthétique du dessin de masques (layout) directement utilisable par tout fondeur. Génère des fichiers

.CIF.

Caltech étant l'abbréviation de California institute of technology.

C.I.S.C Complex Instruction Set Computer. Ordinateur ŕ jeu d'instructions complexes. Par opposition aux ordinateurs RISC (Reduced Instruction Set Computer)

C.L.B : Configurable Logic Bloc (XILINX)

C.L.U.F : Contrat de Licence Utilisateur Final

Coeur : (CORE)

Partie principale de la puce regroupant les fonctions internes du circuit..

S'applique également aux cellules de fortes dimensions (megacell)

tels que les microprocesseurs (coeur de micro).

CMOS : Complementary Metal Oxyde Silicium

C.M.P : Circuit Multi Projets

C.M.S : Composants Montés en Surface

C.N.I.L : Commission Nationale de L'Informatique et des Libertés http://www.cnil.fr

Compilateur :

Logiciel générant automatiquement le layout d'un objet dont il aura seulement suffit de décrire les caractéristiques sous une forme appropriée . Se dit le plus souvent des logiciels de synthèse de chemins de données ( data-path ) (silicon compiler).

Controlabilité :

Evaluation de la facilité d'acheminement d'une donnée de test en un point particulier d'un circuit à partir de ses entrées primaires.

Couverture de fautes:

Mesure la capacité d'un ensemble de test à détecter les pannes potentielles pouvant se produire au sein d'un circuit. S'exprime

le plus souvent sous forme de pourcentage (rapport du nombre de fautes susceptibles d'ètre détectées au nombre de fautes

possibles).

C.P.L.D : Complex Programmable Logic Device

C.S.A : Conseil Supèrieur de l'Audiovisuel mais plutot (Carry Select Adder)

C.S.A.M : Conseil Supérieur de l'Aviation Marchande

Datapath : Chemin des données par opposition au chemin de controle.

Design :Indifféremment : - Schéma sous forme d'une interconnexion

de portes ou de macros. - Activité liée à la conception d'un CI.

DCFL : Direct Coupled Fet Logic

DDR : Double Data Rate (Technique de transmission de données doublant la quantité transmise ŕ chaque cycle d'horloge) D.F.T : Design for test

Technique de conception destinée à optimiser et faciliter le test. D.G.A.C : Délégation Générale de l'Aviation Civile

DGCCRF : Direction Générale de la Consommation de la Concurrence et de la Répression des Fraudes

DIP : Dual - In - Line package

D.M.A Direct Memory Access. Procédé par lequel

on écrit directement dans la mémoire vive sans transiter par le microprocesseur. DNS : Domain Name Server (web)

D.R.C : Design Rule Checking

Driver: :

Drop-in : Structure de test spécifique

répartie sur une tranche de silicium et permettant de vérifier

le bon déroulement de chacunes des étapes de fabrication.

Egalement appelé PCM (Process Control Monitor)

D.U.T : Device Under Test

DVB-T : Digital Video Broadcasting Terrestrial. Transmission terrestre de la TV numérique.

E/B : Echantillonneur / bloqueur

E-Beam : Electron Beam

E.B.C.D.I.C :Prononcer "ebcédic". Extended Binary Coded Decimal Interchange Code. Code ŕ huit bits.

E.C.L : Emitter Coupled Logic

E.D.A : Electronic Design Automation

EDIF : Electronic Design Interface Format

Entrance : (Fan-in) Charge capacitive que présente l'entrée d'un opérateur logique. Ce peut ètre aussi

le nombre n des portes élémentaires connectées

à l'entrée d'une cellule. On dit alors que cette entrée présente une entrance de "n".

E.I.A : Electronic Industries Association

Epic :

Electronic Privacy Information Center

http://www.epic.org

Epic :

Sigle qui apparaissait aussi dans la documentation XILINX.

EPROM : Electrically Programmable Read

Only Memory (Mémoire morte programmable électriquement).

EEPROM : Electrically Erasable Programmable Read Only Memory. EPLD : Erasable Programmable Logic Device E.R.C : Electrical Rule Checking

E.S.D : Electro Static Discharge.Une bonne protection ŕ l'ESD devra aller au dela de 2500 Volts.

ESPRIT : Programme européen d'aide à la recherche et au développement des systèmes de traitement

des informations .

EUREKA : Programme Européen de développement de technologies civiles (commerciales).

Evènement:

EXTEST : External Test. Instruction définie dans le standard Boundary-Scan permettant de tester les connexions sur carte.

FAI : Fournisseur d'Accés ŕ Internet (Provider)

FET : Field

Effect Transistor (Transistor

à effet de champ)

F.F.T : Fast

Fourier Transform (Transformée de Fourier Rapide)

Fil de raccordement (Bond-wire)

Flatpack : Boitier plat utilisé en montage en surface. Féquemment utilisé en applications

militaires et spaciales.

Floorplan : (Plan de masse).

Fondeur : (Fondeur de silicium). Fabricant.

F.U.S.E : Programme Europeen d'aide à

l'intégration de plus d'électronique dans les produits fabriqués.

F.P.G.A : Field Programmable Gate

Array (Prédiffusé programmable)

FQDN : Fully Qualified Domain Name

Front end : Outils de dessin , de description , de

simulation et de vérification d'un design utilisés dans la

phase initiale de saisie. Par opposition aux outils de back end.

FSL : Fond de Solidarité Logement

F.T.P : File Transfert Protocol

Garde :

Distance minimale devant séparer deux éléments d'un

layout pour respecter les règles technologiques du fondeur.

Gate Array : Prédiffusé (Réseau de portes)

G.D.S.II : Norme de description

géométrique des polygones d'un layout (voir aussi CIF )

Gravure : (ETCHING)

GPRS: General Packet Radio Service

GPS: Geo Positionnement par Satellite

Hardware Modeling: Possibilité d'associer un composant

dans une simulation directement par la présence physique de celui-ci.

Cela allège d'autant la représentation informatique. Particulièrement

intéressant lorsqu'on a affaire à un composant complèxe (microprocesseur).

HTTP : Hyper Text Transfert Protocol

HOTSPOT :

Zone couverte par un réseau WI-FI. (La borne d'accés est constituée de plusieurs modiles)

ICONE: : Symbole représentant un opérateur ou une fonction d'une bibliothèque. On représente

cet opérateur dans un schéma par son icone.

IDCODE : IDentity CODE. Instruction définie par le standard Boundary-Scan fournissant une information sur le composant

I.E : Internet Explorer (Le navigateur de Microsoft) - (web)

I.E.E.E : Institute for Electrical and Electronic Engineering

INRIA: Institut National de Recherches en Informatique et Automatique.

INTEST : INternal TEST. Instruction définie par le standard Boundary-Scan qui valide le test interne du circuit.

IOB : Input Ouput Bloc (XILINX)

IP : Internet Protocol (web)

ISP : Internet Service Provider (web)

Initialisation: Séquence de stimuli d'entrée amenant un circuit dans un état déterminé.

JEDEC : Joint Electron Device Engineering Council

J.P.E.G : Joint Photographic Experts Group

J.T.A.G : Joint Test Action Group

J.E.S.S.I : Joint European Submicron Silicon Initiative

JESSICA : JESSI pour la conception d'ASIC.

Au sein du programme JESSI, favorise l'intégration des asic dans les PME-PMI.

L.A.S.E.R : Light Amplifier by Stimulated Emission of Radiation (Amplification de lumičre par émission stimulée de radiations)

Langage M: Language de Modélisation (description comportementale).

Langage L : Langage de Layout (description structurelle).

Layout : Dessin au niveau masques d'un design (Niveau quasi physique du design ).

LCD :Liquid Crystal Display (Affichage ŕ cristaux liquides)

Leaf cell : Cellule de base dans la constitution de blocs.

LETI :

Laboratoire d'Electronique de Technologie et d'Informatique.

L.C.A : Logic

Cells Array (XILINX)

L.C.C.C : Leadless Ceramic Chip Carrier.

LED : Light Emitting Diode (Diode émettrice de lumičre) L.V.S : Layout Versus Schematic

L.P.E : Layout Parasitic Extractor

L.S.B : Least Significant Bit (bit de poids le plus faible, souvent le bit de droite d'un registre)

L.S.I :Large Scale Integration (Intégration ŕ grande échelle) Trčs vite devenu VLSI.

L.U.T : Look up table (Blocs F, G et H dans un CLB chez XILINX)

Masque :

MESFET : MEtal Schottky FET

M.I.C Modulation par Impulsions et Codage. Permettait, en téléphonie, d'étager jusqu'ŕ 30

communications dans la largeur de bande d'une mčme liaison électrique sur une paire de fils. Commençait ŕ poindre le principe

d'émissions par paquets. On affectait, alternativement, ŕ chaque utilisateur une tranche de temps. Temps pendant lequel sa voix

était codée. C'était ce codage numérique qui était émis sur la paire de fils.

M.I.P.S : Million d'Instructions Par Seconde

M.S.B : Most Significant Bit (le bit de poids le plus fort, souvent le bit le plus à gauche d'un registre)

MPEG-II : Movie Picture Expert Group.

Format du codage numérique de séquence vidéo animées (Bonne compression)

MTBF : Meantime before fealure (Temps moyen entre deux pannes d'un circuit)

NETLIST

N.L.I : Non Linéarité Intégrale

N.L.D : Non Linéarité Différentielle

NMOS : Logique utilisant des transistors à canal N (MOS E/D)

OLE : Object Linking Embedding

Pad : (Plot) Electronique de la cellule d'entrée / sortie assurant l'interfaçage avec

l'environnement externe . Comprend les buffers et protections (résistances, diodes de clamping , etc .... ).

P.A.L : Programmable Array Logic

P.I.D : Proportionnel, Intégral, dérivée (Dans une boucle de régulation...)

P.C : Personal computer

PDIP : Plastic Dual - In - Line package

P.G.A : Pin Grid Array

PIN : Personal Identification Number (Code donnant accčs ŕ un portable. Contrecarre les utilisations frauduleuses)

Plan de masse : (Floorplan)

P.L.C.C : Plastic Leadless

Chip Carrier (pour montage en surface -CMS)

Portage : Opération consistant

à passer d'une technologie à une autre. Concerne souvent

l'évolution technologique d'une bibliothèque.

P.L.D : Programmable Logic Device

P.P.P : Points par pouce (Unité servant ŕ caractériser la finesse du grain d'impression d'une imprimante)

P.S.N : Processor Serial Number

Puce : (DIE)

Qualification : Ensemble de tests et de caractérisations

d'un circuit pour vérification du respect des spécifications avant production.

R.A.M : Random Access Memory

R.F.I.D : Radio Frequency Identification Devices. Permet le suivi des objets par le développement des étiquettes communicantes. Mais, attention,

permet aussi la surveillance des individus avec tous les risques de dérapages pas forcément au service de la liberté individuelle.

R.I.A.A : Recording Industry Association of America (Courbe correctrice RIAA dans les amplis)

R.L.A.N :Radio Local Area Network (Réseau local ss fil)

La norme 802.11g (54 Mbits et 2.4 GHz) tend ŕ remplacer la norme 802.11b (11 Mbits et 2.4 GHz)

Reuse L'art de réutiliser les blocs concus pour un précédent design dans un autre design.

Le reuse a pour vocation d'augmenter de façon significative la productivité d'un concepteur ou de son bureau d'études. On a souvent

affaire ŕ des blocs paramétrés qui autorisent l'ajustement au cas particulier en cours d'étude.

Resine : Barrière sensible à la lumière ou à un bombardement d'électrons permettant

le dessin de motifs sur une tranche de silicium (photo resist).

Routage :

S.A.D.T: Structured Analysis and Design Technic.

Saisie graphique : (schematic capture) ou saisie de schéma.

Scan-Path :

SET : Secure Electronic Transaction. Settling time : Temps d'établissement

Setup

Shrink : Opération de réduction des géométries des éléments d'un layout dans

une étape de changement de technologie. Passer par exemple d'une technologie 1,2 micron ŕ 0,8 micron. Il y a alors diminution

des tailles des transistors et autres. (opération inverse : DESHRINK)

SIM : Subscriber Identity Module (Carte ŕ puce intégrée au portable contenant les informations relatives ŕ l'abonnement)

SMS : (Short Message Service)

S.N.R : Signal to Noise Ratio (rapport signal sur bruit)

SIMD : Single Instruction Multiple Data

SMTP : Simple Mail Transfert Protocol

S.O.G Sea of Gates Mer de portes

S.O.I : Silicon

On Insulator Silicium sur isolant

S.O.S : Silicon On

Saphir (Mais aussi: System On Silicon).

SRAM : Static Random Access Memory

SSCCI : Société de

Service en Conception de Circuits Intégrés.

SSL : Secure Socket Layers. Taux de couverture de fautes :

TAP : Test Access Port (boundary-scan)

TCK : Test Clock

(JTAG). Broche d'horloge de synchronisation d'un boundary-scan.

TDI : Test Data Input (JTAG). Broche d'entrée des

données série d'un boundary-scan.

TDO : Test Data Output (JTAG). Broche de sortie des données

série d'un boundary-scan.

TER :Train Express Régional (En perte de vitesse par les temps qui courent)

TMS : Test Mode Select. Entrée accédant au TAP d'un boundary-scan. Niveau

logique conditionnant à chaque coup d'horloge en TCK le cheminement à travers le graphe d'états du TAP.

Testabilité :

Testeur : Machine destinée à tester le circuit en fin de chaine de production.

TILE : Cellule de base (tuile)

TNT Il y a 50 ans c'était "Trinitrotolučne". Particuličrement dangereux ŕ manipuler et ŕ ne

pas mettre entre les mains de n'importe qui (Surtout par les temps qui courent!!!). La moindre petite goutte en chute libre faisant

un grand boummm!!!. De nos jours ce serait plutot "Télévision Numérique Terrestre".

Toggle Rate : Fréquence max, pour une technologie donnée, à laquelle peut commuter une bascule D refermée sur elle-méme

par un inverseur.

T.T.L : Transistor Transistor Logic

UMTS : Universal Module Telecommunication System

URL : Uniform Resource Locator

UMTS: Universal Mobil Telecommunication Systems

Via : Contact,

dans un circuit intégré, entre deux pistes situées

sur des niveaux différents de couches métalliques.

V.M.E : Versa Module Europe (ou BUS VME)

V.H.D.L Very high speed Hardware Description Language.

VITAL : VHDL Initiative Towards Asic Library.

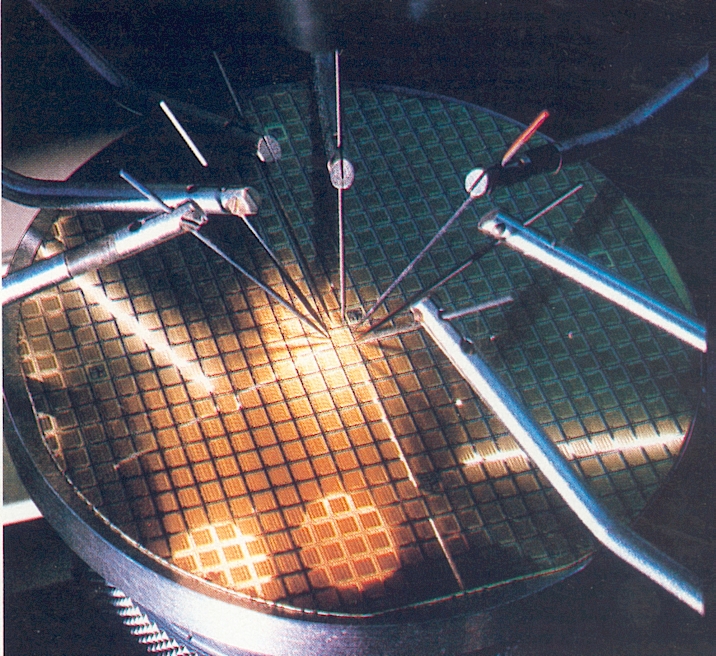

Wafer : Tranche circulaire de silicium ultra pur, sur laquelle seront gravés les circuits à fabriquer.

Ci-contre, un wafer deja gravé sous tests.

WAP : Wireless Application Protocol. Protocole adaptant les pages internet ŕ l'écran d'un portable. C'est l'accčs ŕ l'internet mobile.

WMP : Windows Media Player (PC)

WI FI : WIreless FIdelity Protocoles de communication sans fils entre PC et périphériques

SMTP Simple Mail Transfer Protocol (Protocol pour messagerie électronique)

PO3 Post Office Protocol version 3 (Protocol gérant les réceptions de mails)

PKE Public Key Encryption (Code envoyé par l'expéditeur pour décrypter un fichier)

DES Data Encryption Standard Algorithme de codage le plus connu. (IBM, NSA)

RSA Algorithme de cryptage du nom de ses auteurs(Rivest, Shamir et Adleman). Met en oeuvre des clés asymétriques.

PGP Pretty Good Privacy ("Assez bonne confidentialité") Cryptage asymétrique mis au point par Phil Zimmermann

S-MIME Secure Multipurpose Internet Mail Extension

"Application Specific Integrated Circuit" Michael John Sebastian Smith

"Managing VLSI complexity" Carlo SEQUIN (Un expert apprécié - Berkeley)

"ASIC" P.de HALLEUX - J.P FESTE - D. GIRAULT - RV HONCRAT (Ed Radios)

"Conception et vérifications de circuits VLSI" Y. SAVANIER (Ed. Ecole Polytechnique de Montreal)

"Circuits logiques programmables"

"VHDL du langage à la modélisation" R. AIRAN - JM. BERGE - V. OLIVE - J. ROUILLARD

"Spécifications et conception des ASIC" JP. CALVEZ (Ed Masson)

"Conception des ASIC" P. NAISH - P. BISHOP (Ed. Masson)

"Circuits numériques RJ. TOCCI (Ed. Dunod)

"Electronique numérique" (logique séquentielle) M. GINDRE et D. ROUX (Ed. Mc Graw-Hill)

" logic minimization algorithms for VLSI synthesis" R.K BRAYTON - Kluwer Academic publishers 1985

"ASYL: a rule based system for controller synthesis" Gabrielle SAUCIER, Michel CRASTES de PAULET, P. SICARD

"Optimized layout of MOS cells" Gabrielle SAUCIER , G.THUAU

"VLSI design"

Début

Début

Cette technique a conduit certains fabricants de microprocesseurs ŕ annoncer

des fréquences horloge deux fois plus élevées que les fréquences effectives (Abusif en quelque sorte)

D'ou rapidité des transferts.

Vérification du respect des règles technologiques (Espacement entre les objets,

largeurs de transistors , de pistes , etc ...... )

Porte ou simple buffer dimensionné de façon à

pouvoir commander, dans le respect des performances en vitesse, une charge capacitive souvent élevée.

Début

Début

Faisceau d'électrons extrèmement fin (0,1um) destiné à bombarder la surface d'un wafer pour y dessiner directement les

motifs d'un circuit sans avoir à utiliser de masques.

Format de description de netlists.

Association d'utilisateurs d'Internet aux Etats Unis

(Editor Programmable Integrated Circuit)

Mémoire morte efaçable et programmable électriquement.

Circuit logique effaçable (U.V) et reprogrammable électriquement.

Vérification du design au plan électrique (détection des entrées ou sorties non connectées par exemple (dangling).

Changement d'état d'un noeud au sein d'un circuit à l'occasion d'une simulation. Plus généralement, une commutation qui

appelle un traitement spécifique de la part d'un système.

Début

Début

Fil d'aluminium ou d'or fin reliant les plots du pad ring aux broches externes du boitier. L'épaisseur des fils de raccordement

varie entre 20 et 70 um. Surveiller les effets selfiques.

Organisation topologique optimisée des différents blocs d'un circuit sur le silicium. Dispositions devant faciliter le routage

et optimiser les distributions d'horloge et le passage des alimentations. Limiter les longueurs de fils reliant le coeur aux pads.

C'est le possesseur d'une centrale de technologie apte à fabriquer

le circuit intégré. Etant seul à parfaitement connaitre

les caractéristiques de sa technologie (le process), il a pour obligation

de fournir au client une "Bibliothèque" et peut éventuellement

fournir certains outils de CAO (tool-kit), tout particulièrement les outils de "Back end" .

F.C.P : Fonds Communs de Placements

Début

Début

Marque déposée de GE CALMA .

Début

Début

On parle d'adresse IP pour désigner l'adresse exacte de l'ordinateur qui vient de se connecter

sur la toile.

Cette adresse est codée sur 32 bits (Comprendre: 4 x 8 bits ou 4 octets)

Un octet permettant de coder tout nombre

compris entre 0 et 255, une adresse IP pourra se présenter sous l'apparence ci-aprčs: 125.74.8.210.

Début

Début

Le standard JEDEC définit le format selon lequel doit ètre représenté le fichier de programmation d'un P.L.D (Programmable Logic Device).

Groupe de travail ayant proposé le BOUNDARY- SCAN

Programme Européen de recherche et développment des systèmes

microélectroniques. JESSI est un programme EUREKA

(CEE) mis en place lors de la conférence européenne à

Vienne en Juin 1989. Programme sensé s'ètre arretéen 1996.

Un LASER désigne un faisceau de luničre cohérente. Un véritable concentré de photons pouvant čtre focalisé trčs précisément.

Ce faisceau peut par exemple servir ŕ graver les wafers pour obtention des circuits intégrés.

Il se réfléchit sur les microcavités des disques optiques (CD, DvD) pour y lire les données numériques.

On l'utilisera pour les disques optiques réinscriptibles.

Il permet la transmission de données ŕ haut débit par fibres optiques.

C'est l'apparence finale d'un circuit, celle qu'il aura sur le silicium.

Destiné au montage en surface (CMS)

Il serait étonnant que sur la face avant de votre PC il n'y ait pas une ou deux LED par endroits.

Vérification de la concordance du layout et de la netlist au niveau électrique.

(Continuités électriques par éxemple)

Logiciel d'extraction des valeurs des capacités parasites et de rétro-annotation

dans la netlist .

Plaque photographique de verre représentant les motifs d'un niveau de fabrication d'un circuit (diffusions, interconnexions, contacts,

etc ...)

Début

Début A l'arrivée, il y avait décodage pour restitution en clair de la voix.

A l'émission on mettait en oeuvre un convertisseur analogique / numérique. A la réception était mis en oeuvre un convertisseur numérique / analogique.

A l'arrivée, il y avait décodage pour restitution en clair de la voix.

A l'émission on mettait en oeuvre un convertisseur analogique / numérique. A la réception était mis en oeuvre un convertisseur numérique / analogique.

Fichier consignant la liste des cellules d'un circuit et leur interconnexion.

Décalage de la transition d'un palier par rapport à la transition théorique pour un

C.N.A (Convertisseur Numérique Analogique). (Erreur par rapport à la droite idéale de transfert).

Début

Début

Proposé par INTEL, le PCI s'est imposé comme un standard de transfert de données de

périphériques à unité centrale sur 32

ou 64 bits à 33 ou 66 MHz. Dans l'industrie, c'est par exemple un

sérieux concurrent au bus V.M.E.

Numéro d'identification tatoué sur les processeurs Pentium

III. Numéro parfaitement lisible à partir de tout

site WEB.

Début

Début

Disposition des fils d'interconnexion entre transistors, cellules et blocs d'un CI. L'étape de routage est généralement

assurée par un logiciel qui tendra à optimiser le tracé de ces fils eu égard aux critéres de vitesse et superficie

. Etape généralement précédé d'un placement.

Chemin de test (En fait: Association en série de la totalité

ou d'une partie des bascules d'un design pour en faire un long registre

à décalage devant améliorer notablement la testabilitédu circuit .

Protocole développé par VISA et MASTERCARD. Nécessite le téléchargement d'un logiciel sur votre ordinateur.

Le commercant et l'acheteur sont identifiés et chacun recoit un certificat d'authentification par sa banque.

On prévoit une carte ŕ puce qui sera couplée au protocole SET.

Votre numéron de CB est crypté pendant qu'il transite sur le réseau. Le code n'est cependant pas inviolable.

L'authentification du marchand ou de l'acheteur n'est pas possible.

Début

Début

Chiffre qui rend compte de l'aptitude d'un pattern de test à détecter un maximum de défauts physiques d'un circuit sous

test . C'est un mesure prédictive obtenue lors de l'étape de simulation de fautes . Un taux de couverture raisonnable doit excéder

85% .

Caractérise la plus ou moins grande facilité de tester un circuit ou un bloc. Recouvre les caractéristiques de controlabilité

et d'observabilité du bloc. Elément déterminant de la qualité d'une conception sous l'entière responsabilité

du concepteur.

La technologie d'un testeur est des plus sophistiquée eu égard aux performances en vitesse exigées.

Début

Début

Vecteurs de test (test pattern) :

Suite des valeurs logiques à appliquer à un circuit ou

un bloc pour détecter une ou plusieurs fautes . C'est généralement

le pattern délivré sur les entrées du bloc sur un coup d'horloge.

Standard de communications dans le domaine des cartes industrielles. En concurrence avec le standard PCI.

Bibliothèque de modélisation de l'ensemble des primitives utilisées dans un ASIC. Facilite toute modélisation de netlist.

Est devenu un standard pour tout fondeur et fabricant de FPGA.

Début

Début

VLSI systems series (Addison-Wesley ISBN 0-201-50022-1) (Tout à fait recommandable)

Proceeding of the IEEE

C. TAVERNIER (Ed. Dunod)

Ed. Presse Polytechniques et universitaires romandes (La référence)

IEEE transaction on C.A.D - Nov 1988

IEEE transactions on computers